ScepticMatt

Member

For use in upcoming GPU like Polaris/Pascal and Zen-based APUs that could be used in next-gen consoles.

Key specs:

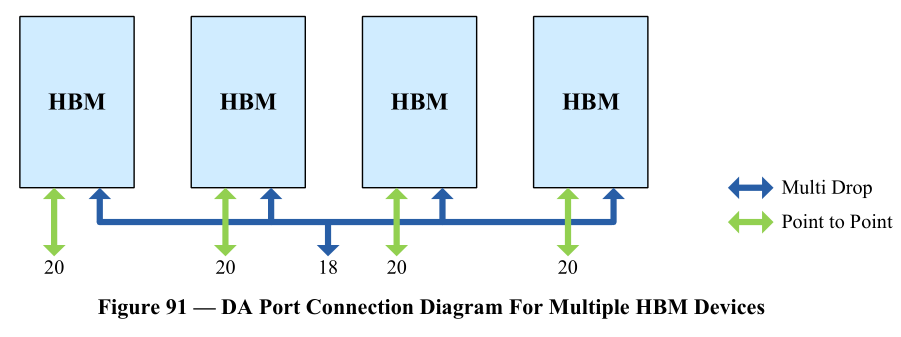

1, 2 or 4 stacks.

1024 bit interface width per stack

up to 8 layers per stack (up from 4) in dual channel mode

up to 1 GB per layer (up from 256 MB)

1 GHz clock (up from 500 MHz)

Scaleable from 1 to 32 GB and 256 GB/s to 1 TB/s.

Press release:

ARLINGTON, Va., USA JANUARY 12, 2016 JEDEC Solid State Technology Association, the global leader in the development of standards for the microelectronics industry, today announced the publication of an update to JESD235 High Bandwidth Memory (HBM) DRAM standard. HBM DRAM is used in Graphics, High Performance Computing, Server, Networking and Client applications where peak bandwidth, bandwidth per watt, and capacity per area are valued metrics to a solutions success in the market. The standard was developed and updated with support from leading GPU and CPU developers to extend the system bandwidth growth curve beyond levels supported by traditional discrete packaged memory. JESD235A is available for free download from the JEDEC website.

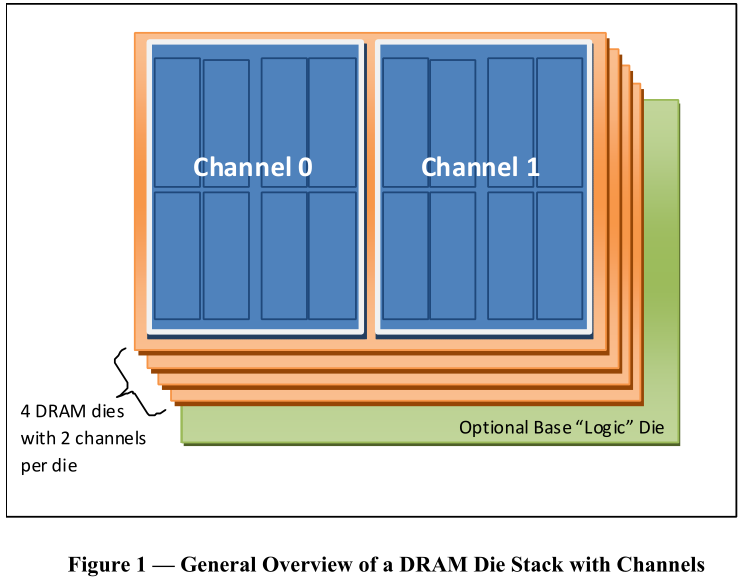

JESD235A leverages Wide I/O and TSV technologies to support up to 8 GB per device at speeds up to 256 GB/s. This bandwidth is delivered across a 1024-bit wide device interface that is divided into 8 independent channels on each DRAM stack. The standard supports 2-high, 4-high and 8-high TSV stacks of DRAM at full bandwidth to allow systems flexibility on capacity requirements from 1 GB 8 GB per stack.

Additional improvements in the recent update include a new pseudo channel architecture to improve effective bandwidth, and clarifications and enhancements to the test features. JESD235A also defines a new feature to alert controllers when DRAM temperatures have exceeded a level considered acceptable for reliable operation so that the controller can take appropriate steps to return the system to normal operation.

GPUs and CPUs continue to drive demand for more memory bandwidth and capacity, amid increasing display resolutions and the growth in computing datasets. HBM provides a compelling solution to reduce the IO power and memory footprint for our most demanding applications, said Barry Wagner, JEDEC HBM Task Group Chairman.

https://www.jedec.org/news/pressrel...ndbreaking-high-bandwidth-memory-hbm-standard